# Performance Analysis of Dual Edge Triggered Memory Cells using Multiple C-Elements

K.Mariya Priyadarshini, Sampad Kumar Panda, R.S. Ernest Ravindran, S Sarvani, P Mohan Vinay, B Suresh Gopi Chand

Abstract: This research paper presents a low conditional discharge(C-element) Flip-Flops that are basic elements in all digital design. The existing circuits are power hunger due to the dynamic and static power dissipation increases. For reducing power consumption C element technique is used to reduce glitches at the data out. Results obtained through 130nm technology shows reduction in energy dissipation and delay. Average dynamic power dissipation of the proposed flip-flop is compare with two existing techniques. Average power of proposed flip-flop is reduced by 28.41% and 36.18% when compared with Latch-Mux flip-flop and Latch-Mux using Celement.

Key Words: Dual Edge Triggering (DET), C-element, Latch-Mux, Flip-Flop.

#### I. INTRODUCTION

Flip-flops are basics storage elements used in many of Very Large Scale Integrated circuits, so they have to be designed with optimized power consumption. This paper presents the design of the Dual edge triggered (DET) flip-flops based on C-element using pass transistor technique. As the technology is scaling from micron technology to deep submicron technology the leakage power is one of the parameter which is effects the circuit performance. By using this technique the leakage power is reduced in the DET Flipflops[1-6].

Manuscript published on November 30, 2019

\* Correspondence Author

Priyadarshini, K.Mariya Department of Electronics Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

R.S. Ernest Ravindran Sampad Kumar Panda, Department of Electronics and Communication Engineering, Koneru Education Foundation, Vaddeswaram, AP, India.,

- S Sarvani, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

- P Mohan Vinay, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, AP, India.

- B Suresh Gopi Chand, Department of Electronics and Communication Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram,

- © The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

The designs presented in this paper were simulated in CMOS 16nm technology using Tanner tool, observed to have superior characteristics such as power consumption and power-delay product (PDP) when compared to existing DET Flip-flops.Like Single edge triggered flipflop, also Dual edge triggered flipflop achieves the same data rate at half the clock frequency and leads to reduce power dissipation of synchronous logic circuits.Instead of using Single edge triggered flipflop, we can make possible for power savings by using dual edge triggered flipflop. A common Dual Edge Triggered (DET) flipflop design called Latch Mux DET flipflop and it has two input latches multiplexed to single output.A C-element is a three terminal device with two inputs and oneoutput[7],[9].When all the inputs of Celements are same, the values of inputs and outputs are same, otherwise the previous output value is preserved. This device acts as a latch which can be reset and set with suitable combinations of signal levels at the input. New techniques of overlapping clocking schemes are analyzed in [11]. As nanotechnology is occupying equal space along with MOS technology nanometer devices for increasing clocking efficiency are presented in [12]. A Detailed scrutiny of various single edge triggered memory cells is studied in [13].

Low power very large scale integrated (VLSI) circuits have a great potential in the digital electronics. Dual-edge triggered (DET) flip-flops came into existence in the place of single edge triggered (SET) flip-flops[16-19]. As the DET flip-flops achieve the same data rate as of the SET flip-flops at half the clock frequency resulting in low power dissipation in the synchronous logic circuits. Latch-MUX DET flip-flop design is the basic design of the DET flip-flop, which consists of two latches at input where the latches are level-triggered by opposite clocks, Output of these latches are multiplexed to the final output stage through a multiplexer[20-23].

One of the latches is transparent to the output for every change at the output, In the presence of the glitches at the input the power consumption of the flip-flops will be greatly affected by these glitches. The Conditional toggle (CT\_C) Celement flip-flop is one of the alternative DET flipflop design that can reduce the adverse effect of input glitches at the output. Leakage power is one the primitive to considered during the design of VLSI circuits in deep sub-micron technology; there are many techniques such as Dual sleep and Dual slack techniques forreduction of leakage power.

# Performance Analysis of Dual Edge Triggered Memory Cells using Multiple C-Elements

#### **II.EXISTING WORKS**

Simulations have been performed on three different DET flip-flop designs. The designs are:

- 1) Latch MUX DET design in [10]

- 2) Latch-MUX design, that uses a C-element at the output to perform the function of a MUX in [8]

- 3) Implicit-Pulsed DET flip-flop in [4]

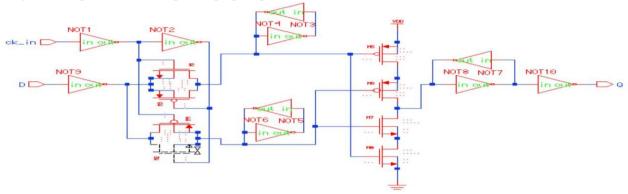

#### Latch Mux Design:

Dual edge triggered flip flops usually consists of two latches and they are multiplexed to one output for proper operation.

State of flip flop is changed by level triggering method. This result in a transparent latch following the changes that occurs in its input signal. It consumes more power and gives less performance. Here clocking activity results in more power dissipation when compared to transitions occurring in input signals. Circuit work here is based on selection of input clock signal. It involves transmission gate for transferring the value of D input to the output signal Q. It is similar to latch-mux single edge triggered flip flop. But they differ in arrangement of latches.

Fig.1 Latch Mux Flip flop

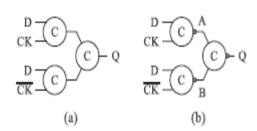

## **Latch Mux Design using C Element**

The logic C element which is mainly used for capturing memory is used to perform the function of multiplexer in this design. Latches which are at higher and lower level receive input for operation. C-element shown in Fig: 2 acts as an inverter when both of its inputs are at same logic level. The weak structure used at the output has two functionalities. The C element's output is retained when PMOS and NMOS transistors are in an off condition. State of output is refreshed even in the presence of large amount of leakage current. Charge sharing issues that occur in circuit are eliminated by the back to back connected inverter circuit.

Fig: 2 Logic circuit of C-Element

.Fig.2 Latch Mux Flip flop using C-Element

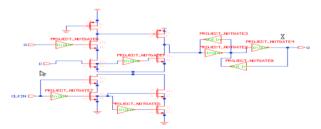

#### III. PROPOSED WORK

Our proposed flip flop has 20 transistors and is having two data paths. The upper data path consists of a Single Edge Triggered flip-flop implemented using pass transistors. This works on positive edge. The lower data path consists of a negative edge triggered flip-flop implemented using pass transistors. When the input gets a positive clock pulse then the D input is transmitted in the upper data path and this one is constructed by using pass transistor logic. This operation is divided into two cases i.e., When the positive edge of the clock is applied to the circuit then the input is applied to both the paths but input data flows through upper data path through data transfer through few inverters and nmos transistors but any edge pulse '15' input is zero output 'Q' gets at output of '15' inverter. When the negative edge of clock is applied to the circuit then the input is applied to both the paths but input data flows through lower data path through data transfer through few inverters and nmos. In this case also input of '15 'is zero then output directly gets one but this operation is explained using idle case, in practical case we can get some power consumption appearing at output side due to the switching transactions and some leakage powers. In this method DET flip-flop consists of 20 transistors and also power consumption is little bit large compare to previous methods

Fig.4 Proposed DET Flip Flop

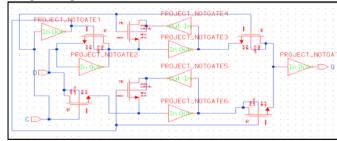

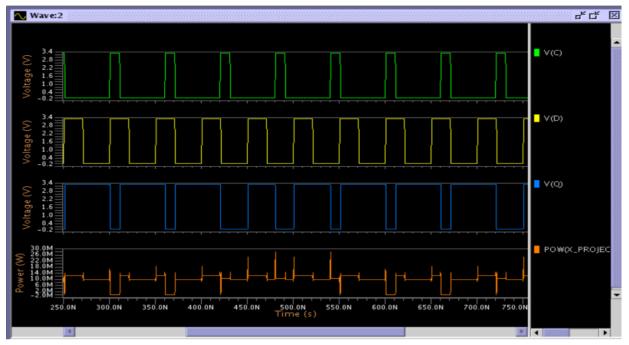

#### IV. SIMULATION RESULTS

This section describes the performance of the proposed design using done using Mentor Graphics tool wave forms are shown for the proposed flip-flop in Fig: 4. From the output waveforms of fig:4 it is clear that the proposed Dual Edge Triggered flip-flop gives a glitch free output with minimum power dissipation and delay.

Fig: 4 Output Wave form of proposed technique showing glitch free output.

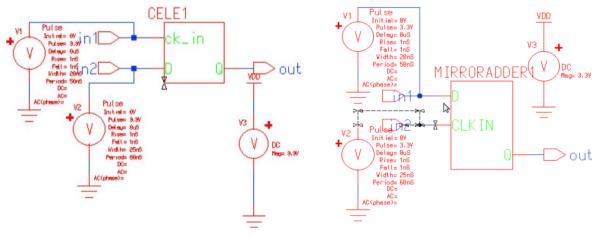

Fig: 5 Test Bench circuit of Latch Mux Flip flop using C-**Element considered for simulation**

Fig: 6 Test Bench circuit of Latch Mux Flip flop considered for simulation

Table: 1 Power Dissipation Comparison of proposed and Existing Flip-Flops

| Types of Flip-Flops | Various types of Power Dissipation Values |           |          |              |

|---------------------|-------------------------------------------|-----------|----------|--------------|

|                     | Maximum                                   | Minimum   | Average  | Peak to Peak |

| proposed            | 26.468μW                                  | 87.540 nW | 7.097 μW | 24.46 μW     |

| Latch-Mux DETFF     | 54.75 μW                                  | 90.09 nW  | 11.12 μW | 54.47 μW     |

| Latch-Mux using C-  | 32.264 μW                                 | 88.19 nW  | 9.914 μW | 31.38 μW     |

| Element             |                                           |           |          |              |

From the above table:1 it is clear that proposed flip-flop shows very less values in all concerns of power dissipation. When comparing proposed technique with Latch-Mux Flipflop in maximum and peak to peak power dissipation, but the average power dissipation has no much difference. Latch-Mux Flip-Flop using C-element shows less power

values than Latch-Mux DETFF, but proposed technique is efficient than existing two techniques.

The following table:2 shows the delay analysis from table:2 we conclude that Latch Mux Flip-Flop using C-Element shows less delay when compared to proposed technique. This is due to fast switching structure of C-element.

# Performance Analysis of Dual Edge Triggered Memory Cells using Multiple C-Elements

Table: 2 Delay Comparison of proposed with existing techniques

| Types of Flip-Flops           | Delay Types       |             |            |

|-------------------------------|-------------------|-------------|------------|

|                               | Propagation Delay | Set-up Time | Hold Time  |

| Proposed                      | 1.41 nsec         | 12.17nsec   | 9.17nsec   |

| Latch-Mux using C-<br>Element | 65.240 psec       | 32.05 psec  | 24.56 psec |

| Latch-Mux DETFF               | 26.3652 nsec      | 45.97 nsec  | 37.09 nsec |

#### V.CONCLUSION

Two novel DET flip-flops have been discussed. The new proposed design is compared with existing circuits and we conclude that power dissipation and number of transistor count is improved. But the delay of the proposed circuit lies in between Latch-Mux with C-element and without Celement. The proposed circuit is also free from glitches which can be used for high performance scenarios. Voltage scaling performance can also be done to further study the performance to more logic depth.

## REFERENCES

- StepanLapshev and S. M. Rezaul Hasan, "New Low Glitch and Low Power DET Flip-Flops Using Multiple C-Elements", IEEETrans. Very Large Scale Integer.(VLSI) Syst, June 27'2016

- N. Nedovic and V. G. Oklobdzija, "Dual-edge triggered storage elements and clocking strategy for low-power systems," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 13, no. 5, pp. 577-590, May 2005.

- A. G. M. Strollo, E. Napoli, and C. Cimino, "Analysis of power dissipation in double edge-triggered flip-flops," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 8, no. 5, pp. 624-629, Oct.

- P. Zhao, J. McNeely, P. Golconda, M. A. Bayoumi, R. A. Barcenas, and W. Kuang, "Low-power clock branch sharing double-edge triggered flip- flop," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 3, pp. 338-345, Mar. 2007.

- J. Tschanz, S. Narendra, C. Zhanping, S. Borkar, M. Sachdev, and V. De, "Comparative delay and energy of single edge-triggered and dual edgetriggered pulsed flip-flops for high-performance microprocessors," Proc. Int. Symp. Low Power Electron. Des., 2001, pp. 147-152.

- Mounica J., Ganesh G.V., Design of a nonvolatile 8T1R SRAM Cell for instant-on operation ,2016, International Journal of Electrical and Computer Engineering, Vol. 6, Issue: 3, pp. 1183 - 1189, ISSN 20888708

- Paradhasaradhi D., Satya Priya K., Sabarish K., Harish P., Narasimharao G.V., Study and analysis of CMOS carry look ahead adder with leakage power reduction approaches ,2016, Indian Journal of Science and Technology, Vol. 9, Issue: 17, ISSN 9746846.

- S. V. Devarapalli, P. Zarkesh-Ha, and S. C. Suddarth, "A robust and low power dual data rate (DDR) flip-flop using C-elements," in Proc. 11th Int. Symp. Quality Electron. Des. (ISQED), Mar. 22-24 2010, pp. 147-150.

- Noorbasha F., Manasa M., Gouthami R.T., Sruthi S., Priya D.H., Prashanth N., Rahman M.Z.U., FPGA implementation of cryptographic systems for symmetric encryption,2017 Journal of Theoretical and Applied Information Technology, Vol:95, issue:9, pp: 2038-2045, ISSN: 19928645

- Noorbasha F., Hari Kishore K., Naveen T., Sai Anusha A., Manisha Y., Revathi K., Manasa M. .," Implementation of modified Feistel block cipher for OTP generation using Verilog HDL ", 2018, Progress In Electromagnetics Research M ,Vol: 63 ,Issue: ,pp: 163 to:: 173 ,DOI: ,ISSN: 19378726

- R. Hossain, L. D. Wronski, and A. Albicki, "Low power design using double edge triggered flip-flops," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 2, no. 2, pp. 261-265, Jun. 1994.

- A. Bonetti, A. Teman, and A. Burg, "An overlap-contention free true single-phase clock dual-edge-triggered flip-flop," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 24–27 2015, pp. 1850–1853.

- M. Alioto, E. Consoli, and G. Palumbo, "Analysis and comparison in the energy-delay-area domain of nanometer CMOS flip-flops: Part I-Methodology and design strategies," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 19, no. 5, pp. 725-736, May 2011.

- 14. V. Stojanovic and V. G. Oklobdzija, "Comparative analysis of master slave latches and flip-flops for high-performance and low-power systems," IEEE J. Solid-State Circuits, vol. 34, no. 4, pp. 536-548, Apr. 1999.

- 15. M. Alioto, E. Consoli, and G. Palumbo, "Analysis and comparison of variations in double edge triggered flip-flops," in Proc. 5th Eur. Workshop CMOS Variability (VARI), Palma de Mallorca, Spain, 2014, pp. 1-6.

- M. Shams, J. C. Ebergen, and M. I. Elmasry, "Modeling and comparing CMOS implementations of the C-element," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 6, no. 4, pp. 563-567, Dec. 1998.

- BalaDastagiri N., Hari Kishore K., Reduction of kickback noise in latched comparators for cardiac IMDs ,2016, Indian Journal of Science and Technology, Vol. 9, Issue: 43, ISSN 9746846

- Vikas K., Sunithamani S., Yagnika M., Siva Krishna S., Avanthi S. .," Study and analysis of novel RF MEMS switched capacitor ", 2018, International Journal of Engineering and Technology(UAE), Vol: 7 ,Issue: 1.5 ,pp: 37 to:: 41 ,DOI: ,ISSN: 2227524X .

- Paradhasaradhi D., Satya Priya K., Sabarish K., Harish P., Narasimharao G.V., Study and analysis of CMOS carry look ahead adder with leakage power reduction approaches ,2016, Indian Journal of Science and Technology, Vol. 9, Issue: 17, ISSN 9746846

- Supriya M.V., Noorbasha F., Implementation of low-power flip-flops using c-element ,2016, International Journal of Engineering and Technology, Vol. 8, Issue: 2, pp. 692 - 699, ISSN 23198613

- K Mariya Priyadarshini, Dr.R.S Ernest Ravindran R.Vinay Kumar, R.Harish, S.S.Sai bhattar, T. Pavan sri kalyan, "Design and implementation of Dual edge Triggered shift registers for IOT applications", IJSTR, Volume 10, Issue 10, August 2019.

- R. S. Ernest Ravindran, K Mariya Priyadarshini, Dangeti Peda Manikya Pavana Teja, Popuri Nikhil Chakravarthy, Peruboyina Dharma Teja "Design of RAM using Quantum Cellular Automata (QCA) designer", International Journal of Scientific and Technology Research Volume 8, Issue 8, August 2019, Pages 1385-1390.

- K Mariya Priyadarshini, R. S. Ernest Ravindran "A Novel Two Fold Edge Activated Memory Cell with Low Power Dissipation and High Speed", International Journal of Recent Technology and Engineering (IJRTE) ISSN: 2277-3878, Volume-8, Issue-1, May 2019.

- Vasudha M., Pravallika B.S., Kiran C.S., Subhani P., Rakesh Chowdary G., Prakash M.D., Kishore K.H., Ramakrishna T.V., Design and performance analysis of a nonvolatile memory cell,2017 Journal of Advanced Research in Dynamical and Control Systems, Vol:9, issue: Special Issue 14, pp: 2320-2327, ISSN: 1943023X

Journal Website: www.ijrte.org