# Design Combinational Circuit of Reversible Circuits in Emerging Technologies for HCI

Ravitesh Mishra, Sanjeev Gupta

Abstract:- The first aim of the thesis is to design feature selection and classification algorithms to distinguish between binary and multiple mental states. These algorithms must produce an optimal performance in terms of accuracy and computational time so that it can be used in real-time applications. Secondly, to design BCI control strategies using reversible combinational ckt like multiplexer, multiplier, adder/sub-tractor for real-time thought control of a human computer interaction (HCI). Reversible logic has emerged as one of the most important approaches and more prominent technology nowadays. Power is the main concern for development and growth of modern VLSI designs.

Keywords: HCI, BCI, Reversible Gate, Combinational Circuit

## I. INTRODUCTION

The capacity to convey and collaborate with machines utilizing thought has caught the creative mind of humankind over numerous ages. Ongoing progresses in intellectual neuroscience and mind mapping innovations enable us to interface straightforwardly with the human cerebrum. Using sensors one can screen the physical procedures happening inside the mind that relates to a certain type of considerations [1]. At first, scientists utilized these advances to construct braincomputer interfaces (BCIs) [2] to give restoration to individual's physical incapacities and improve their way of life. BCIs give a correspondence channel that doesn't depend on the cerebrum's typical practical pathways of fringe nerves and muscles. Here, the clients expressly control their mind movement to control an outside gadget like a PC or a prosthetic arm. Such innovations give another rent of life to individuals experiencing obliterating neuromuscular wounds and neurodegenerative infections, for example, amyotrophic parallel sclerosis, loss of motion, cerebral paralysis and amputees [3]. As of late, the field of utilization of BCIs began including PC gaming [4], correspondence [5], robot control in mechanical and military Scientists taking a shot applications. computerinterference (HCI),

Manuscript published on November 30, 2019.

\* Correspondence Author

**Sanjeev Gupta,** Dean Academics Department of EC RabrindraNath Tagore University Bhopal, India

**Ravitesh Mishra Assistant** Professor Department of EC RabrindraNath Tagore University Bhopal, India

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

consistently endeavors to increment the correspondence data transfer capacity and quality between the connections happening between the human and the PC (or robot). These scientists investigate the different perceptions also, multimodal showings with the goal that PCs may use however many tactile channels as could be expected under the circumstances to send information to a human. Likewise, they have structured and created equipment and programming advancements to build

the information stream to the PC in the most limited conceivable time. Also, these analysts are endeavoring to find data about client state and purpose by noticing their physiology, conduct and their working condition. Such data helps the framework to powerfully adjust and give better help to the client for the main job [6]. BCI specialists extraordinarily advantage from the expertise created in the field of HCI where the frameworks depend entirely on interfacing with the cerebrum as the control component. In like manner, BCIs are currently settled enough with the end goal that HCI scientists may incorporate them while structuring novel input methods (particularly in conditions with requirements on ordinary engine development), while estimating generally slippery subjective or passionate wonders in assessing our interfaces, or then again while attempting to construe client state to assemble versatile frameworks [7].

#### II. HUMAN-COMPUTER INTERACTION

The development in Human-Computer Interaction (HCI) field has not exclusively been in nature of association, it has likewise experienced diverse expanding in its history. There have been different PC driven transformations before. It might incorporate the PCs from 1960 to 2000. A diagrammatic portrayal is as appeared in Figure 1. In 1960s one centralized computer was utilized by numerous clients. In any case, the circumstance changes in 1980s. Work area PCs are generally utilized by the clients for various reason like charging in shops, keeping records, and so forth. In 2000 a solitary client is associated with various PCs for doing their work. Presently versatility is happened in 2000 and client can do his work from wherever. Be that as it may, we are looking sooner rather than later for example is in 2020. It might resemble the fourth picture as appeared in Figure 1. We are expecting such a change in HCI [8].

Toward the beginning of the 21st century, HCI was an interdisciplinary field which has experienced huge changes. Regarding a science or a control, these progressions have happened over a brief span. HCI now envelops numerous ways of thinking, points of view what's more, kinds of mastery.

# Design Combinational Circuit of Reversible Circuits in Emerging Technologies for HCI

There are various and covering gatherings of analysts, some underscoring structure, others assessing, but then others client displaying. These specialists all work inside a mind boggling space, each inspecting various parts of human-PC collaboration. Various strategies are utilized, contingent upon various objectives [9].

Figure 1: Illustration of Changes in HCI from 1960s to 2000 and expecting 2020 being as vivid as 4th image

### III. PROPOSED METHODOLOGY

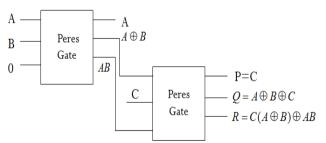

**RAS:** - RAS is depending on number of bits. 2-bit addition is used to Peres gate (PG) and 3-bit addition is used to double Peres gate (DPG). Structure for 3-bit addition is shown figure 2.

Figure 2: Structure of DPG

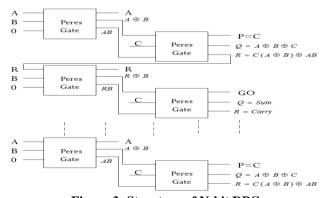

Figure 3: Structure of N-bit DPG

DPG is used to three inputs A, B and C and three output P, Q and R. P=C is the garbage output of DPG because 3-bit addition only two output i.e. 'SUM' and 'CARRY'. 'SUM' is represented by Q and 'CARRY' is represented by R.

Structure of N-bit DPG is shown figure 3. In N-bit structure, first DPG 'CARRY' is connected to second DPG input. In this paper 4-bit adder is implemented then four DPG are used.

#### RM:-

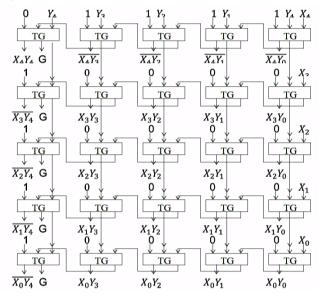

RM is based on two concepts, first one is generation of all partial products (PP) of multiplication in parallel using TG and then secondary these terms are added together using multi operand addition (MOA) algorithm using DPG and PG.

Figure 4: PP of RM

Once PP terms are generated, the following step is the MOA to adding the bits of each column. This can be done by using DPG and the PG shown figure 5.

Figure 5: MOA for RM

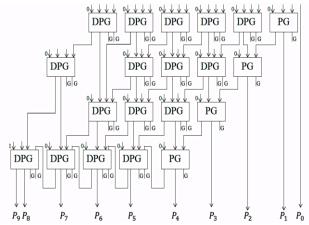

#### RMUX:-

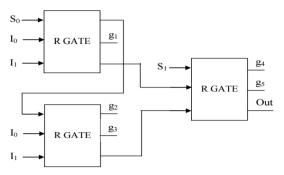

The main use of multiplexer is for data selection, translation of parallel data into serial one. Circuit implementation for the 4×1 RMUX is shown in Figure 6 is done in a reversible manner by using reversible logic R gate.

Figure 6: Structure of 4×1 RMUX

#### IV. SIMULATION RESULT

More in particular, we have grown new rubbish free circuits for expansion and are working towards a general duplication circuit. We have likewise consolidated various tasks together to execute a reversible number-crunching rationale unit. With these and other waste free number-crunching circuits it is conceivable to outline bigger reversible processing frameworks. For instance, we have executed discrete lossless changes by updating these with a lifting plan. We have additionally demonstrated the outline of a reversible figuring engineering and executed this utilizing just reversible rationale doors. While, these are still little frameworks, with assist improvement it ought to be conceivable to utilize comparable methodologies to execute considerably bigger frameworks.

Table 1: Compare Result-I

| Table 1. Compare Result-1 |          |                 |                   |                   |  |  |  |

|---------------------------|----------|-----------------|-------------------|-------------------|--|--|--|

| Reversible Designs        |          | Quantum<br>Cost | Garbage<br>Output | Constant<br>Input |  |  |  |

| Reversible                | Existing | 15              | 5                 | 0                 |  |  |  |

| Multiplexer               | Proposed | 12              | 5                 | 0                 |  |  |  |

| Reversible<br>DEMUX       | Existing | 15              | 2                 | 3                 |  |  |  |

|                           | Proposed | 12              | 2                 | 3                 |  |  |  |

| Reversible<br>Decoder     | Existing | 27              | 1                 | 6                 |  |  |  |

|                           | Proposed | 23              | 1                 | 6                 |  |  |  |

| Reversible<br>Encoder     | Existing | 27              | 9                 | 4                 |  |  |  |

|                           | Proposed | 22              | 9                 | 4                 |  |  |  |

| Reversible<br>Multiplier  | Existing | 341             | 61                | 46                |  |  |  |

|                           | Proposed | 237             | 46                | 46                |  |  |  |

| Reversible                | Existing | 36              | 9                 | 5                 |  |  |  |

| Adder/                    | Proposed | 30              | 10                | 5                 |  |  |  |

| Sub-tractor               |          |                 |                   |                   |  |  |  |

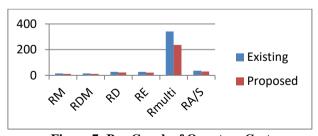

Figure 7: Bar Graph of Quantum Cost

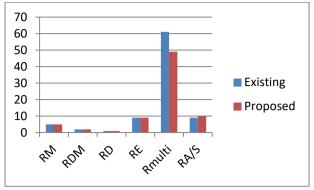

Figure 8: Bar Graph of Garbage Output

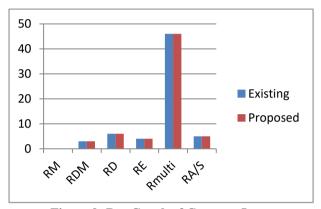

Figure 9: Bar Graph of Constant Input Table 1: Compare Result-II

| Reversible Designs                  |          | Gate<br>Count | Total<br>Cost | Power   |

|-------------------------------------|----------|---------------|---------------|---------|

| Reversible<br>Multiplexer           | Existing | 21            | 41            | 2135.4  |

|                                     | Proposed | 12            | 29            | 1707.6  |

| Reversible<br>DEMUX                 | Existing | 21            | 41            | 2135.4  |

|                                     | Proposed | 12            | 26            | 1707.6  |

| Reversible<br>Decoder               | Existing | 35            | 63            | 4126.7  |

|                                     | Proposed | 23            | 47            | 3557.5  |

| Reversible<br>Encoder               | Existing | 35            | 71            | 4126.7  |

|                                     | Proposed | 22            | 50            | 3130.5  |

| Reversible<br>Multiplier            | Existing | 45            | 447           | 31724.3 |

|                                     | Proposed | 45            | 328           | 33725.1 |

| Reversible<br>Adder/<br>Sub-tractor | Existing | 36            | 81            | 5122.8  |

|                                     | Proposed | 30            | 70            | 4269.0  |

### V. CONCLUSION

Proposed a combinational element with the improved performance in terms of design parameters improves the execution time of overall architecture is present. Proposed designs are compared in terms of cost, garbage output, constant input, delay, gate count, power, area and a total cost to the existing design. Proposed multiplexer improve the instruction fetch unit performance and instruction decode unit. Logic style use is reversible in nature provide the regularity for implementation using random and proposed logic design gives out efficient design implementation which improves the performance of overall architecture and increases its speed.

## Design Combinational Circuit of Reversible Circuits in Emerging Technologies for HCI

#### REFERENCES

- Z. Wang, S. Liu, J. Zhang, S. Chen, and Q. Guan, "A spatio-temporal crf for human interaction understanding," IEEE Transactions on Circuits and Systems for Video Technology, vol. 27, no. 8, pp. 1647– 1660, 2017.

- X. Shu, J. Tang, G.-J. Qi, Y. Song, Z. Li, and L. Zhang, "Concurrenceaware long short-term sub-memories for person-person action recognition," in CVPRW, 2017.

- X. Wang and Q. Ji, "Hierarchical context modeling for video event recognition," IEEE Transactions on Pattern Analysis and Machine Intelligence, vol. 39, no. 9, pp. 1770–1782, 2017.

- H. Hajimirsadeghi and G. Mori, "Multi-instance classification by maxmargin training of cardinality-based markov networks," IEEE Transactions on Pattern Analysis and Machine Intelligence, vol. 39, no. 9, pp. 1839–1852, 2017.

- Y. Kong and Y. Fu, "Close human interaction recognition using patchaware models," IEEE Transactions on Image Processing, vol. 25, no. 1, pp. 167–178, 2016.

- M. Ibrahim, S. Muralidharan, Z. Deng, A. Vahdat, and G. Mori, "A hierarchical deep temporal model for group activity recognition," CVPR, 2016.

- Q. Ke, M. Bennamoun, S. An, F. Bossaid, and F. Sohel, "Spatial, structural and temporal feature learning for human interaction prediction," arXiv, 2016.

- Gopi Chand Naguboina and K. Anusudha, "Design and Synthesis of Combinational Circuits Using Reversible Decoder in Xilinx", IEEE International Conference on Computer, Communication, and Signal Processing, Issue 01, pp. 01-06, IEEE 2017.

- Marcin Bryk, KrysztGracki, PawalKerntop and Marek Pawlowski, "Encryption using reconfigurable reversible logic gate and its simulation in FPGAs", International Conference on Mixed Design of Integrated Circuits and Systems, Issue 06, pp. 203-206, IEEE 2016

Umeshkumar, LavishaSahu, Uma Sharma, "Performance Evaluation

- Umeshkumar, LavishaSahu, Uma Sharma, "Performance Evaluation of Reversible Logic Gates", International Conference on ICT in Business Industry & Government, Issue 11, pp. 01-04, IEEE 2016.

- Y. Kong and Y. Fu, "Max-margin action prediction machine," IEEE Transactions on Pattern Analysis and Machine Intelligence, vol. 38, no. 9, pp. 1844–1858, 2016.

- Y. Cao, D. P. Barrett, A. Barbu, S. Narayanaswamy, H. Yu, A. Michaux, Y. Lin, S. J. Dickinson, J. M. Siskind, and S. Wang, "Recognize human activities from partially observed videos," in CVPR, 2013.