# Low-Power Adiabatic Computing with Modified Quasi Static Energy Recovery Logic of MQSERL 4x4 multiplier

# M.Mailsamy, V.Rukkumani, K.Srinivasan, B.Sharmila

Abstract: This work depends on another methodology for limiting vitality utilization in semi static vitality recuperation rationale of Modified Quasi Static Energy Recovery Logic (MQSERL) circuit which includes enhancement by expelling the non-adiabatic misfortunes totally. Vitality recouping hardware dependent on adiabatic standards is a promising system driving towards low power superior circuit plan. The productivity of such circuits might be expanded by lessening the adiabatic and non-adiabatic misfortunes drawn by them amid the charging and recuperation tasks. In this paper, execution of the proposed rationale style is broke down and contrasted and CMOS in their agent inverters, entryways, flip- flop and snake circuits. Every one of the circuit was reproduced by test system of TANNER TOOL in 0.18µm innovation. In our proposed inverter the vitality proficiency has been enhanced to practically 30% and 20% up to 20MHz and 20fF outside load capacitance in contrast with CMOS and MQSERL circuits individually. Our proposed circuit gives vitality proficient execution up to 100 MHz and in this way it has ended up being utilized in superior VLSI hardware.

Index Terms: Component; Adiabatic logic; Power consumption; Quasi Static Energy Recovery Logic (QSERL); CMOS logic.

## I. INTRODUCTION

With the developing prerequisite of convenient correspondence many research have been done to lessen vitality scattering [1]-[4], among them adiabatic rationale procedure [5] is extremely encouraging. In adiabatic circuits vitality scattering happens because of adiabatic and non-adiabatic misfortunes. On the off chance that we bring down the rate of charging, lesser measure of intensity is drawn from the source and lesser will be adiabatic misfortunes. Non-adiabatic misfortunes happen because of the voltage on.

# Revised Manuscript Received on 30 July 2019.

\* Correspondence Author

Mayilsamy M\*, Dept. of Electronics and Communication, CMS College of Engineering and Technology ,Coimbatore,India.

Rukkumani V, Dept. of Electronics and Instrumentation Engineering, Sri Ramakrishna Engineering College, Coimbatore, India.

Srinivasan K Dept. of Electronics and Instrumentation Engineering, Sri Ramakrishna Engineering College, Coimbatore, India.

Dr.B.Sharmila, Assistant Professor (Sr.G) in the Department of Electronics and Instrumentation Engineering at Sri Ramakrishna Engineering College, Coimbatore

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

The majority of the adiabatic circuits have these non-adiabatic misfortunes because of the voltage drop over the diodes or inadequate vitality recuperation. The essential thought for lessening adiabatic misfortunes is that; clock transient time T is kept a lot bigger than characteristic time consistent RCL of the gadget [6]. Non-adiabatic misfortunes are limited by recouping the vitality put away in load capacitances [7]. The vitality in charging the heap capacitances is recouped amid releasing and put away for reuse. In adiabatic rationale circuits time differing voltage supply is utilized so that the nodal capacitance are charged or released at a consistent current which makes voltage drop practically unimportant, while in CMOS rationale circuits we utilize steady DC voltage source. The word 'adiabatic' is utilized in a reversible thermodynamic process [8] where a change is done as such that no gain or loss of warmth or vitality happens. By making the change procedure moderate the warmth or vitality misfortune can be made just about zero in a perfect world. Lately numerous adiabatic rationale structures have been proposed which chip away at a similar hypothesis however have distinctive circuit structures and multifaceted nature. The semi static vitality recuperation rationale (QSERL) circuit [9] endeavors to diminish the disadvantages of the past vitality recuperation rationale (ERL) families because of its static rationale similarity circuit structure, decreased exchanging action and number of intensity tickers however it have downside of in-power and yield coasting due to the interchange hold stages.

Integral vitality way adiabatic rationale (CEPAL) gives enhancement to the QSERL circuit since it needn't bother with input manager to evacuate coasting yield which thusly enhances zone and power overhead [10]. Likewise its throughput is better (twice) than QSERL. Be that as it may, because of the additional MOSFET diodes in charging and releasing way somewhat bigger power dissemination than QSERL circuits happen. Because of these difficulties with detailed adiabatic rationale circuits [11-19] we propose altered semi static vitality recuperation rationale (MQSERL) circuit. MQSERL acquires every one of the upsides of as of late detailed QSERL circuits with extra enhancement in power sparing by decreasing the non-adiabatic misfortunes just as adiabatic misfortunes. We have planned and recreated different MQSERL based rationale circuits and their exhibitions have been assessed and contrasted and some detailed adiabatic circuits and traditional CMOS circuits. This paper contains four segments. Segment 1 bargains the presentation part.

Retrieval Number: B1736078219/19©BEIESP DOI: 10.35940/ijrte.B1736.078219 Journal Website: www.ijrte.org

1896

# Low-Power Adiabatic Computing with Modified Quasi Static Energy Recovery Logic of MQSERL 4x4 multiplier

Segment 2 portrays the proposed vitality recuperation rationale (MQSERL) circuit and it's working. In area 3 we have reenactment results and dialog. The area 4 condenses the end.

## II. PROPOSED ENERGY RECOVERY LOGIC CIRCUIT

## 2.1. ENERGY RECOVERY LOGIC CIRCUIT

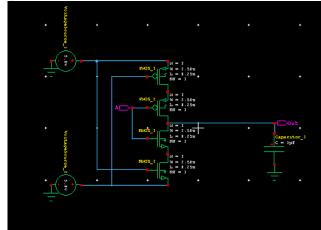

The circuit of altered semi static vitality recuperation rationale (MQSERL) is appeared in Figure 1(a). It is made out of with two correlative sinusoidal power timekeepers (VA and VA<sub>bar</sub>), a charging PMOS transistor (P1) whose door is associated by the power clock VA , and a P-arrange in charging way, and a releasing NMOS transistor (N1) whose entryway is associated by the power clock VAbar , and a N-organize in releasing way. The power clock (VA<sub>bar</sub>) is in stage while the other clock (VA) is 180 degree out of stage. The sinusoidal clock charges/releases the heap capacitance nearly gradually than the triangular or trapezoidal power timekeepers. We have talked about in past area that we can upgrade control productivity of adiabatic rationale circuits by guaranteeing that how gradually the nodal capacitances are charged or released in this manner control dissemination is limited by utilizing these sinusoidal tickers. The top to crest voltage of intensity tickers VAbar and VA is 1.8 V. The transistor (P1) in the draw up system and transistors (N1) in the draw down system are utilized rather than the diode (which was utilized in QSERL circuit) for lessening the non-adiabatic misfortunes. Power clock (VAbar) controls the ON and OFF time of transistor (N1) and (VA) controls the ON and OFF time of transistors (P1). The perceptible wellspring of intensity dissemination in QSERL circuits was because of the MOSFET diode's limit voltage drop (which is non-adiabatic misfortune) though in the proposed MQSERL circuit, the principle wellspring of influence misfortune is because of the ON opposition of channels of MOSFET transistors P1 and N1 [12]. The hardships as a result of the ON impediment of P1 and N1 are on a very basic level lower than the mishaps in view of the limit voltage drop through diodes and all in all setbacks can also be brought somewhere near cutting down the charging speed. Along these lines by using transistors (P1 and N1), control spread is very diminished interestingly with the diode based circuits. At any rate we can't empty the power dissipating absolutely in light of the non reversible nature of the proposed circuit.

## 2.2. CIRCUIT OPERATION

The activity of the circuit is separated into two phases dependent on the supply clock phases, evaluation and hold. In assessment stage VABAR step by step increments from low to high voltage while VA bit by bit diminishes from high to low voltage, though in hold stage VABAR bit by bit diminishes from high to low and VA increments from low to high voltage as appeared.

In assessment stage, whenever yield hub ( $V_{out}$ ) is at LOW rationale and the P tree is turned ON; stack capacitance (CL) is charged through PMOS transistor (P1) delivering HIGH rationale at the output. Whereas whenever yield hub ( $V_{out}$ ) is at HIGH rationale and N tree turns ON, releasing and reusing to the power clock (VA) by means of NMOS transistor (N1) happens, creating LOW yield rationale. In hold stage, VABAR diminishes from high to low and VA increments

Retrieval Number: B1736078219/19©BEIESP DOI: 10.35940/ijrte.B1736.078219 Journal Website: <u>www.ijrte.org</u> from low to high and when they comes to underneath the edge voltage of P1 and N1 the two turns OFF in this way no advances appeared at the yield. Dynamic exchanging is decreased due to the hold stage, which will again diminish the vitality dissemination.

## 2.3. PROPOSED ENERGY RECOVERY LOGIC NOR GATE

The proposed MQSERL NOR entryway is appeared in Figure 2(a). This circuit is produced using two PMOS transistors (M1 and M2) and two NMOS transistors (M3 and M4).

Figure 1. Proposed energy recovery logic INVERTER

Figure 2. Proposed energy recovery logic NAND Gate

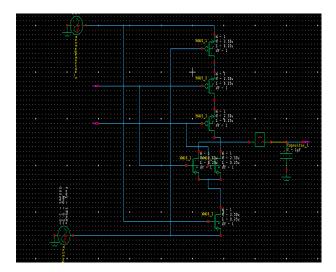

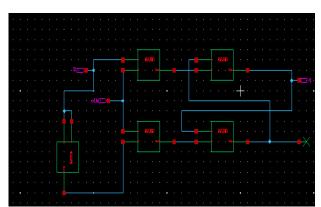

#### 2.4. PROPOSED ENERGY RECOVERY LOGIC NAND GATE

The proposed MQSERL NAND entryway is appeared in Figure 3(a). The circuit is produced using two PMOS transistors (M1 and M2) tied in parallel and two NMOS transistors (M3and M4) which are associated in arrangement.

Yield stack capacitance is charged/released through charging/releasing pMOS/nMOS transistors P1 and N1 whose door is specifically associated with sinusoidal power clock (VA and VABAR separately). M1 and M3 doors are associated together with data and M2 and M4 doors are associated with another data B.

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

1897

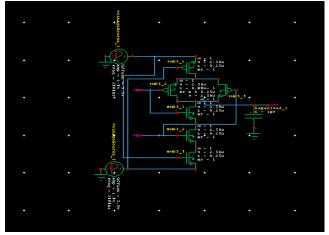

## 2.5. PROPOSED ENERGY RECOVERY LOGIC XOR GATE

The proposed MQSERL XOR entryway is appeared in Figure 4(a). Its' circuit is produced using a P coordinate with four pMOS transistors (M1, M2 tied in parallel and M3, M4 associated in parallel) and a N connect with four nMOS transistors (M5 and M7 associated in parallel with M6 and M8).

A charging pMOS transistor P1 and a releasing nMOS transistor N1 is likewise utilized which are controlled by sinusoidal power timekeepers (VA and VABAR individually). M1 and M6 doors are associated with data and M3 and M5 with VA. Anyway M2 and M8 entryways are associated with data B and M4 and M7 with B.

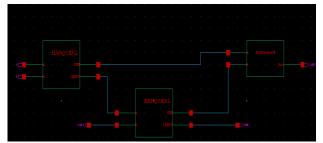

2.6. PROPOSED ENERGY RECOVERY LOGIC 4 BIT HALF ADDER AND FULL ADDER

The MQSERL full viper comprises of two MQSERL half adders and an OR gate. The square dimension outline of our MQSERL half adder is given in Figure 5(a).(b) It is produced using a XOR entryway and one AND gate. By using this method total delay and power consumption to be reduced. 2.7. PROPOSED ENERGY RECOVERY LOGIC D FLIP-FLOP

The proposed MQSERL D flip slump is appeared in Figure 6, it is produced using two MQSERL 3 input NAND entryways and two MQSERL 2 input NAND doors and a MQSERL inverter circuit. From the simulation of various logic like CMOS, QSERL, IQSERL and Proposed MQSERL with a common frequency is calculated.

Table I shows that the proposed MQSERL circuits have practically 36% or more prominent vitality sparing to the traditional CMOS circuits aside from half snake (25.7% vitality saving).Comparison of proposed MQSERL and CMOS circuits at (fA,  $fA_{bar}$ )=200MHz, balance =50MHz

Figure 3. Proposed energy recovery logic NAND Gate circuit of MQSERL.

Figure 4. Proposed energy recovery logic XOR Gate circuit of MQSERL

Figure 5(a). Half Adder circuit of MQSERL

Figure 5 (b).Full Adder circuit of MQSERL

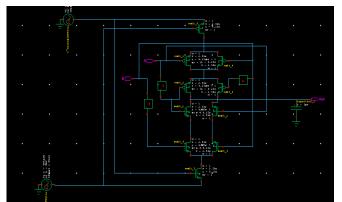

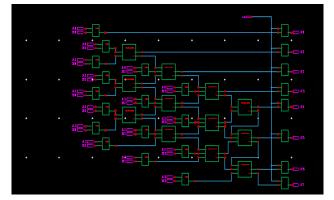

## 2.8. PROPOSED MQSERL 4X4 MULTIPLIER CIRCUIT.

A 4×4 piece MQSERL cluster multiplier is constructed and designed to demonstrate the handiness of the new methods of family for expansive circuits. This architecture contains of 16 MQSERL AND gate, 4 MQSERL half adders, 8 IQSERL full adders, and 8MQSERL D flip-flops as appeared in Figure 7(a). D flip-flops are used to store the 8-bit signals. The stage is finished with recreation parameters as W/L of PMOS 540/180 nm and NMOS 240/180 nm Technology, and data rate was kept multiple times the power clock rate (in IQSERL). From Figure 7 (b), the modified data and output timing waveforms check the 4-bit multiplier basically. Modified results for the proposed IQSERL multiplier are contrasted and CMOS and as of (QSERL) multipliers [17-19] utilizing a similar rationale usage, level with exchanging likelihood of sources of data, and a similar reproduction condition. The data and supply frequencies are continuously all the while from 0.1MHz to 20MHz, and comparing power dispersals for the multipliers have been estimated. IQSERL multiplier has huge power sparing to the CMOS and QSERL multipliers.

Retrieval Number: B1736078219/19©BEIESP DOI: 10.35940/ijrte.B1736.078219 Journal Website: www.ijrte.org

# Low-Power Adiabatic Computing with Modified Quasi Static Energy Recovery Logic of MQSERL 4x4 multiplier

As recurrence builds, the power sparing of IQSERL to the CMOS and QSERL multipliers diminishes as appeared in. At 0.05MHz 98% sharing in power when contrasted with the QSERL multiplier and 94% power sharing to the CMOS multiplier are achieved. At 20MHz the power sufficiently to the QSERL multiplier is 7% though to the CMOS multiplier is 11%. As recurrence goes higher, the resistive scattering increases, so control sparing is less.

After a specific high recurrence (here 20MHz), mistaken vield rationales are gotten, so for bigger complex circuits, our MOSERL circuit is constrained in some high recurrence go. Additionally from the design of proposed MQSERL inverter circuit as in Figure 7, we can sum it up for multiplier circuit likewise that, for a given execution, gadgets can be littler for a CMOS multiplier circuit than the MQSERL multiplier circuit. Thus the proposed MQSERL circuit is progressively reasonable for some particular applications where speed and territory are not basic. Since a  $4 \times 4$  bit cluster multiplier is a huge complex circuit, so number of transistors on a chip (transistor check) is likewise a critical parameter to be examined. In Table II, we have given the similar investigation of transistor check of our proposed multiplier with others. It might be seen that the proposed IQSERL rationale requiring less transistors is similar to the CMOS, while IQSERL rationale have less transistor checks than QSERL. Thus it needs less mind boggling format plan and can be utilized to fabricate bigger circuits on a device chip.

# Figure 7(b). MQSERL 4 × 4 bit Array Multiplier Circuit Transient response.

Energy dissipation in µW Circuits NO XO Half Fu D NAN R R adde Flip-f inverte D 11 Gate Gate ad r chain Gate r lop der CMOS 28.8 11.26 7.34 31.6 48.2 15 100.4 9.4 QSERL 15.7 8.6 9.02 30.0 34.5 14 92.3 0.2 IQSERL 1.65 3.2 8.4 263 28.3 116 17 9 1.2 1.1 Propose 2.1 2.8 11 17 26 MOSER 39.2 36.3 55.3 38.2 25.6 43. 48.1 %Energy Saving 3

TABLE I ENERGY DISSIPATION IN DIFFERENT LOGIC CIRCUITS

Figure 6. Proposed energy recovery logic D flip- flop

TABLE II COMPARISION OF DIFFERENT LOGIC CIRCUITS WITH VARIOUS FREQUENCIES

| Frequency(MHz) | 0.01                           | 0.1 | 1   | 10  | 20  | 33.<br>3 | 50  |

|----------------|--------------------------------|-----|-----|-----|-----|----------|-----|

| Logic          | Power dissipation in $\mu W$   |     |     |     |     |          |     |

| CMOS           | 0.09                           | 0.1 | 0.4 | 3.3 | 6.6 | 10.      | 16. |

|                |                                | 2   | 0   | 2   |     | 9        | 4   |

| QSERL          | 0.02                           | 0.1 | 0.6 | 3.6 | 6.2 | 8.9      | 11. |

|                |                                | 0   | 6   | 9   |     | 5        | 7   |

| IQSERL         | 0.01                           | 0.0 | 0.1 | 1.9 | 4.8 | 8.9      | 15. |

|                |                                | 2   | 3   | 2   |     | 2        | 2   |

| Proposed       | 0.05                           | 0.0 | 0.0 | 1.7 | 4.1 | 8.9      | 13. |

| MQSERL         |                                | 1   | 8   |     |     | 0        | 3   |

|                | Delay in ns                    |     |     |     |     |          |     |

| CMOS           | 55.4                           | 3.5 | 1.3 | 1.5 | 1.5 | 1.4      | 1.4 |

|                |                                |     | 7   | 2   |     | 8        | 7   |

| QSERL          | 421                            | 522 | 64. | 9.3 | .69 | 4.1      | 4   |

|                | 0                              |     | 4   | 8   |     | 0        |     |

| IQSERL         | 1.92                           | 6.2 | 4.5 | 2.5 | 2.0 | 1.8      | 1.6 |

|                |                                | 4   | 3   | 6   | 7   |          | 8   |

| Proposed       | 1.8                            | 5.2 | 3.4 | 1.4 | 1.9 | 1.6      | 1.3 |

| MQSERL         |                                |     | 5   | 6   |     |          |     |

|                |                                |     |     |     |     |          |     |

| Frequency(MHz) | Power Consumption (Microwatts) |     |     |     |     |          |     |

| CMOS           | 4.99                           | 0.3 | 0.5 | 5.0 | 9.9 | 16.      | 24. |

|                |                                | 8   | 5   | 5   |     | 1        | 1   |

| QSERL          | 84.2                           | 52. | 42. | 34. | 35. | 36.      | 38. |

|                |                                | 2   | 5   | 6   | 3   | 7        | 5   |

| IQSERL         | 0.02                           | 0.1 | 0.5 | 4.9 | 9.9 | 16.      | 25. |

|                |                                | 2   | 9   | 2   | 4   | 0        | 5   |

| Proposed       | 0.1                            | 0.9 | 0.4 | 3.2 | 8.3 | 14.      | 20. |

| MQSERL         |                                |     |     |     | 7   | 3        | 2   |

Retrieval Number: B1736078219/19©BEIESP DOI: 10.35940/ijrte.B1736.078219 Journal Website: <u>www.ijrte.org</u>

1899

## **III. CONCLUSION**

Table II shows the comparison between various logic with various working frequency ranges. The frequency selected for all the circuits varies from 0.01 MHz to 50 MHz because in that region only we have drastic change in power dissipation, power consumption and delay. All the above values were calculated and displayed. From the tabulated value it is observed that the total power dissipation, Delay and power consumption the proposed method MQSERL performs well in all circuit present in a multiplier. The reenactment results and relative execution assessment uncovered that control dispersal in the MQSERL rationale family is impressively lower than the CMOS and the detailed adiabatic (QSERL) family; subsequently the proposed MQSERL family beats and gives practically 20% or more noteworthy power sparing over CMOS and QSERL up to 50MHz for the MQSERL.

## ACKNOWLEDGMENT

This research was supported and carried out at Department of Electronics and Instrumentation Engineering, Sri Ramakrishna Engineering College, Coimbatore. We would like to thank our Management, Director (Academics), Principal for supporting us with the infrastructure to carry out the research work.

#### REFERENCES

- Cihun-siyong Alex Gong, Muh- Tihan Shiue, Ci-Tong Hong, And Kai-Wen Yao, (2008), "Analysis and Design of an Efficient Irreversible Energy Recovery Logic in 0.18-µm CMOS", IEEE Transaction on Circuits and Systms, Vol. 55, No. 9, pp. 2595-2607.

- Sathe V.S., Juang-Ying C., Papaefthymiou M.C, (2007), "Energy efficient Ghz-Class Charge-Recovery Logic", IEEE Journal of Solid-State Circuits, Vol. 42, No. 1, pp. 38–47.

- Shipra Upadhyay, R.A. Mishra, R.K. Nagaria and S.P. Singh, (2013) ,"DFAL: Diode Free Adiabatic Logic Circuits", International Scholarly Research Network: ISRN Electronics, Hindawi, Vol. 2013,pp. 1-12.International Journal of VLSI design & Communication Systems (VLSICS) Vol.4, No.4, August 201330

- Sompong Wisetphanichkij, Kobchai Dejhan, (2009) "The Combinational and Sequential Adiabatic Circuit Design and Its Applications", Circuits, Systems & Signal Processing, Vol. 28, pp. 523–534. and System, Vol. 52, No. 8, pp. 1580-1589.

- N.S.S. Reddy, M. Satyam, and K.L. Kishore, (2008), "Cascadable Adiabatic Logic Circuits for Low- Power Applications", IET Circuits, Devices & Systems, Vol. 2, No. 6, pp. 518–526.

- Wang Pengjun and Yu Junjun, (2007), "Design of Two-Phase Sinusoidal Power Clock and Clocked Transmission Gate Adiabatic Logic Circuit", Journal of Electronics (China), Vol. 24, No. 2, pp. 225-231.

- Nazarul Anuar, yashuhiro Takahashi, and Toshikazu Sekine, (2010), "Two Phase Clocked Adiabatic Static CMOS Logic and its Logic Family", Journal of Semiconductor Technology and Science, Vol.10, No.1, pp. 1-10.

- Mehrdad Khatir, Alireza Ejlali, Amir Moradi, (2011), "Improving The Energy Efficiency of Reversible Logic Circuits by The Combined Use of Adiabatic Styles", Integration the VLSI Journal, Elsevier, Vol. 44, pp. 12-21.

- Subodh Wairya, R.K. Nagaria & Sudarshan Tiwari, (2012), "Performance analysis of High Speed Hybrid CMOS Full Adder Circuits for low voltage VLSI Design", VLSI Design, Hindawi, Vol. 2012, article ID 173079, pp.1-18.

- Nazarul Anuar, Vashuhiro Takahashi, and Toshikazu Sekine, (2012), "LSI implementation of a lowpower 4x4-bit array two-phase clocked adiabatic static CMOS logic multiplier", Microelectronics Journal, Elsevier, Vol. 43, pp. 244-249.

- Shipra Upadhyay, R. K. Nagaria and R.A. Mishra, (2012), "Complementary Energy Path Adiabatic Logic based Full Adder Circuit", Journal of World Academy of Science, Engineering and Technology (WASET), Vol. 66, pp.161-166.

Retrieval Number: B1736078219/19©BEIESP DOI: 10.35940/ijrte.B1736.078219 Journal Website: www.ijrte.org

- S.Wairya, R. K. Nagaria, and S. Tiwari, "Performance analysis of high speed hybrid CMOS full adder circuits for low voltage VLSI design," VLSI Design, Article ID173079, pp. 1–18, 2012. [13] V. S. Sathe, J.-Y. Chueh, and M. C. Papaefthymiou, "Energyefficient GHz-class charge-recovery logic," IEEE Journal of Solid-State Circuits, vol. 42, no. 1, pp. 38–46, 2007.

- S. Wisetphanichkij and K. Dejhan, "The combinational and sequential adiabatic circuit design and its applications," Circuits, Systems, and Signal Processing, vol. 28, no. 4, pp. 523–534, 2009.

- M.-E.Hwang, A. Raychowdhury, and K. Roy, "Energy-recovery techniques to reduce on-chip power density in molecular nanotechnologies," IEEE Transactions on Circuits and Systems I, vol. 52, no. 8, pp. 1580–1589, 2005.

- P.Wang and J.Yu, "Design of two-phase sinusoidal power clock and clocked transmission gate adiabatic logic circuit," Journal of Electronics, vol. 24, no. 2, pp. 225–231, 2007.

- N. S. S. Reddy, M. Satyam, and K. L. Kishore, "Cascadable adiabatic logic circuits for low-power applications," IET Circuits, Devices and Systems, vol. 2, no. 6, pp. 518–526, 2008.

- C.S. A.Gong,M.-T. Shiue, C.-T.Hong, andK.-W. Yao, "Analysis and design of an efficient irreversible energy recovery logic in 0.18 μmCMOS," IEEE Transactions on Circuits and Systems, vol. 55, no. 9, pp. 2595–2607, 2008.

- N. Anuar, Y. Takahashi, and T. Sekine, "Two phase clocked adiabatic static CMOS logic and its logic family," Journal of Semiconductor Technology and Science, vol. 10, no. 1, pp. 1–10, 2010.

- S. Upadhyay, R. K. Nagaria, and R. A.Mishra, "Complementary energy path adiabatic logic based full adder circuit,"A Journal of World Academy of Science Engineering&Technology, vol. 66,pp. 161–167, 2012.

- M.Khatir, A. Ejlali, and A. Moradi, "Improving the energy efficiency of reversible logic circuits by the combined use of adiabatic styles," Integration, the VLSI Journal, vol. 44, pp. 12–21, 2011.

- N. A. Nayan, Y. Takahashi, and T. Sekine, "LSI implementation of a low-power 4×4-bit array two-phase clocked adiabatic static CMOS logic multiplier," Microelectronics Journal, vol. 43, no. 4, pp. 244–249, 2012.

- V.Rukkumani and N.Devarajan, "Power Efficient Design of Amplifier using Submicron Technology ' International Journal of Mechanisms and Robotic Systems, Inderscience Publishers, Vol.2, No. 1, 2014, pp. 1 – 16.

- V.Radhika,K.Bhaskaran, "High Resolution DPMW Clustered Architecture for digitally Controlled DC-DC Converter using FPGA", Springer 2018.

- V.Rukkumani, K,Srinivasan and M.Saravanakumar, "Design and Analysis of SRAM cells for low Power Reduction using Low Power Techniques" Region 10 Conference (TENCON),22<sup>nd</sup> Nov 2016.

#### **AUTHORS PROFILE**

Mayilsamy has received her Bachelor's Degree in Electronics and Communication Engineering from Government College of Technology, Coimbatore in the year 2008.. He has received her Master's degree in VLSI Design from Anna University of Technology, Coimbatore in 2010. Presently, He is working as

Assistant Professor in the Department of Electronics and Communication Engineering at CMS college of Engineering and Technology, Coimbatore. He has 10 years 6 months of experience in teaching. His research interests are VLSI Design, Electronic Devices and Circuits.

1900

**Dr.V.Rukkumani** has received her Bachelor's Degree in Electronics and Instrumentation Engineering from Government College of Technology, Coimbatore in the year 2004. Upon graduation she started her career as Lecturer in Department of Electronics and Instrumentation Engineering at Sri Ramakrishna Engineering College, Coimbatore in 2005. She has received her Master's degree in VLSI Design from Anna

University of Technology, Coimbatore in 2009. She received her Ph.D. Degree in Electrical Engineering from Anna University, Chennai in the year 2015.

# Low-Power Adiabatic Computing with Modified Quasi Static Energy Recovery Logic of MQSERL 4x4 multiplier

Presently, she is working as Associate Professor in the Department of Electronics and Instrumentation Engineering at Sri Ramakrishna Engineering College, Coimbatore. She has 11 years 6 months of experience in teaching. Her research interests are VLSI Design, Transducers and Industrial Instrumentation. She is the member of IEEE, Life member of ISTE and ISOI. She has published 15 technical papers in International Journals, 04 International Conferences and 12 National Conferences.

K.Srinivasan received his Bachelor's degree in Electronics and Communication Engineering from VLB Janakiammal College of Engineering and Technology, Coimbatore and ME in Process Control and Instrumentation Engineering from Annamalai

University, Chidambaram in 1996 and 2004 respectively. He has completed Ph.D degree from Anna University, Chennai in 2012 under the faculty of Electrical Engineering. He has 18 years of experience in the field of Electronics, Instrumentation and Image & video processing. He published 11 technical papers in refereed International journals among which 4 papers are listed in Anna University Chennai website and also he has published 2 papers in National journals, 9 in International conferences and 11 in National conferences. He published a book titled Digital image processing by Sai publishers, Chennai.He acted as Chair person and Technical comferences. He is reviewer for many peer reviewed journals like IET Image processing, Inderscience, ICTACT Journals etc. Also he holds the membership of many professional bodies such as IEEE, IE, ISTE, IETE and ISOI.

Dr.B.Sharmila completed her Ph.D degree in Electrical Engineering under Anna University, Chennai in the year 2013.She completed her Post Graduate degree in Applied Electronics from Maharaja Engineering College at Coimbatore under the control of Anna University, Chennai in the year 2004. She completed her

Under Graduate degree in B.E in Electronics and Instrumentation Engineering from Tamilnadu College of Engineering at Coimbatore under Bharathiar University in the year 2000.She has secured University Second rank during her Under Graduate Programme.

She began her career as a Software Engineer at Vigil Software Pvt. Ltd, Bangalore from October 2000 to May 2001. She then started her career as a lecturer in the Department of Electronics and Instrumentation Engineering at Maharaja Engineering College from June 2001 to July 2002. She then continued as an Assistant Professor in the Department of Electronics and Instrumentation Engineering, at Tamilnadu College of Engineering from January 2004 to May 2006 and from May 2007 to September 2007. Later she joined as an Assistant Professor (Sr.G) in the Department of Electronics and Instrumentation Engineering at Sri Ramakrishna Engineering College, Coimbatore from 1st September 2007 to 30th November 2012. Then she was promoted as an Associate Professor in the Department of Electronics and Instrumentation Engineering from 1st December 2012 onwards.

Her areas of interest are Advance Control Systems and Network Control System. She has published 6 papers in International journals, 4 papers in International Conferences and two papers in national conferences

Retrieval Number: B1736078219/19©BEIESP DOI: 10.35940/ijrte.B1736.078219 Journal Website: <u>www.ijrte.org</u>