# Four Array PSK Using Xilinx Simulator

Kunal S. Thaker, Kuldeep B. Shukla, Yash K. Sharma, Reenav M. Shukla

Abstract: for any long distance transmission modulation is the basic need for any transmission. At the progress of transmission information frequency will occupy with the carried frequency. Four array PSK work with frequency with four different phase, and then it will transmit in the digital world. With the help of quad phase; overall bandwidth will be decreasing at the end of the four array PSK transmission with less noise. Finally it will give highly accurate output with less bandwidth and long distance transmission of the respective signal. It also consumes low power with Compaq size for the purpose of communication. Xilinx is the software for the rationale of modified any block as well as adjoins some new blocks when required.

Index Terms: Xilinx Simulator, Four Array PSK, Passivefilter, Field Programmable Gate Array.

## I. INTRODUCTION

Modulation is the prime part of any wireless system at the time of communication. Whenever any data will transmit with different aspects with secure destination and reduce noise then use antenna as a required object for wireless communication. For that purpose, use different type of techniques where Frequency Division Multiplexing is one of the admired and appropriate techniques in wireless transmission data. Because of need of long distance transmission many models are planned to design to reduce as well as remove such kind of inappropriate planning output. To decide the suitable signal (as information as well as carry) is also a part of communication. And for this sine wave is the most preferable wave for broadcast. But this (sine) wave under in analogy term so analog circuits are work as a modulation part and stability is directly or indirectly depend upon analog physical circuitry, temperature humidity etc. Hence, to make design vigorous and impervious physical structure which provide stable output and also provide low power requirement of the system. It works on higher bit rate in the analogy system. The blocks which are provide to fulfill the Four Array PSK FPGA based model in Xilinx simulator are 4X1 multiplexer, one timepiece & four holdup blocks to produce four phases then the output is drinkable by the analog filter to produce smooth sinusoidal wave at the output.

#### Revised Manuscript Received on 30 September 2013.

Correspondence Author

Kunal S. Thaker, Electronics and Communication Department, RGPV, Sehore, Bhopal, India.

Kuldeep B. Shukla, Electronics and Communication Department, SAL-ITER, Ahmedabad, India.

Yash K. Sharma, Electronics and Communication Department, SAL-ITER, Ahmedabad, India.

Reenav M. Shukla, Electronics and Communication Department, Sagar IRT, Bhopal, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license <a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>

#### II. ANALYSIS

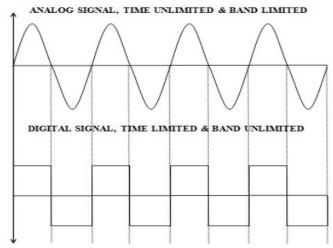

As per fabrication on doped gate area implementation increase need of modulation blocks and fictitious constitution becomes more imperative for mixing signals. And another scenario of communication process the input signal is analog and the problem of that signal it only perform on band limited only. But the signals which perform under in band limited is also time unlimited [1].

In communication if analog signals transmit in the real world then it inhabit limited bandwidth for unlimited time. In digital world analog signals are converted into the digital signals. But again the problem is that the digital signal is time limited but band unlimited. If this signal perform in the digital world then it occupy all the bandwidth for particular time.

Whenever multiply those two frequency it behaves countless evolution for unbounded time. That is why, converted digital signal to the smooth analog signal and this smooth analog signal is known as four array PSK.

# III. OPSK PROCESS

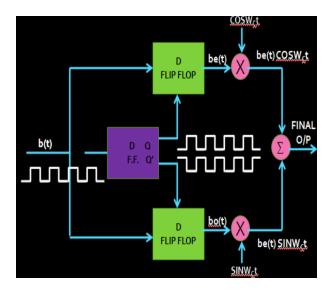

Data will transmit to the pair of D-Flip Flop where D-Flip Flop is known as *Delay-Flip Flop*. Due to folding output of this flip flop it turns out two array PSK which is also known as BPSK (Binary Phase Shift Keying). But for applying latch flip flop need a clock for generate a required data. In quad phase generation of the data take a bit pair in a sequence with even odd procedure. Then back and forth process of D-Flip Flop gives even odd series of the input data. [2]

But for generating quad phase multiply cos ωt with even sequence of the data and multiply sin ωt with odd sequence of the data with 90 degree phase shift of oscillation. This 90 degree phase shift produce another two phase and generate quad sequence. And this quad output will summarized by adder and produce Four Array Phase Shift Keying.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved

## IV. MODEL PROCEDURE IN XILINX

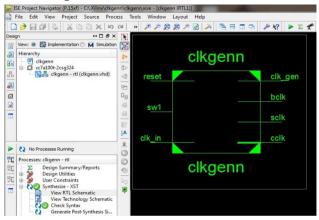

## A. Clock generator

Clock generator generates the clock for start the pairing sequence of D-Flip Flop in this causing plan. Table gives description of clock generation. [6]

## TABLE- CLOCK GENERATOR

| Name of the<br>Terminals | Input /<br>Output | Description of the<br>Terminals                               |

|--------------------------|-------------------|---------------------------------------------------------------|

| Reset                    | Input             | Reset all the previous data                                   |

| sw1                      | Input             | Sequential Width 1 which takes 2bit pair in transmitting data |

| clock in                 | Input             | Input frequency work as a clock                               |

| Clock gen                | Output            | Generation of clock                                           |

| Bclk                     | Output            | Binary clock                                                  |

| sclk                     | Output            | Sine Clock                                                    |

| cclk                     | Output            | Cosine clock                                                  |

The previous data which are already under in the Four Array PSK it will reset by the clock generator reset pin. SW1 is notified as a sequential width 1 which is helpful to take the pair of the data sequence. Clock in represent fixed frequency which is applicable by the user. Due to SW1 and clock in it produce clock generator bclk sclk cclk at the output side sequence.

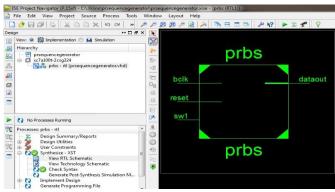

#### B. Pseudorandom Generator

Pseudorandom sequence generator generates the oscillation generator clock to the sine and cosine signals.

# TABLE-PSEUDORANDOM GENERATOR

| Name of the<br>Terminals | Input /<br>Output | Description of the<br>Terminals                               |

|--------------------------|-------------------|---------------------------------------------------------------|

| Bclk                     | Input             | Binary clock                                                  |

| Reset                    | Input             | Reset all the previous data                                   |

| sw1                      | Input             | Sequential Width 1 which takes 2bit pair in transmitting data |

| Dataout                  | Output            | Generate the output data                                      |

Above table formulate to generate the data sequence at the terminal of data out.

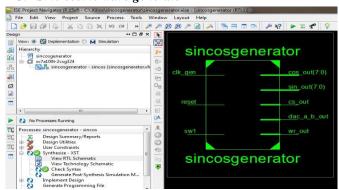

# C. Sine cosine wave generator

| Name of the<br>Terminals | Input /<br>Output | Description of the Terminals                                  |

|--------------------------|-------------------|---------------------------------------------------------------|

| Reset                    | Input             | Reset all the previous data                                   |

| sw1                      | Input             | Sequential Width 1 which takes 2bit pair in transmitting data |

| Clock gen                | Input             | Generation of clock                                           |

| Cos_out (7:0)            | Output            | Output of even term with 8 bit series                         |

| Sine_out (7:0)           | Output            | Output of odd term with 8 bit series                          |

| Cs_out                   | Output            | Clock order comparator                                        |

| Dac_a_b_out              | Output            | Digital to analog run generator of series a and b             |

| Wr_out                   | Output            | Write signal output                                           |

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved

Take 14 bit data progression as input sequence and then it divided into the two series known as a even series and odd series which multiply cosine term and sine term respectively. Clock order comparator compares those two sequences for checking error of the even odd Fourier.

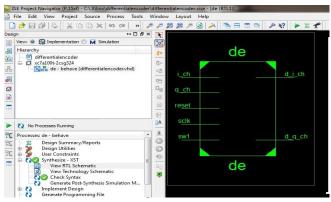

## D. Differential Encoder

Differential Encoder differentiates the sequence with even odd series and creates two phase phenomenon. And these two series produce sequence in the phase difference 180 degree with respect to previous sequence.

# **TABLE-DIFFERENTIAL ENCODER**

| Name of the<br>Terminals | Input /<br>Output | Description of the<br>Terminals |

|--------------------------|-------------------|---------------------------------|

| i_ch                     | Input             | Input channel                   |

| q_ch                     | Input             | Quad Channel                    |

| Reset                    | Input             | Reset all the previous          |

|                          |                   | data                            |

| Sclk                     |                   | Sine Clock                      |

| sw1                      | Input             | Sequential Width 1              |

|                          |                   | which takes 2bit pair in        |

|                          |                   | transmitting data               |

| D_i_ch                   | Output            | Digital in phase channel        |

| D_q_ch                   | Output            | Digital quad phase              |

|                          |                   | channel                         |

Input and Quad channel data produce the data sequence of in and out furrier sequence for a particular data. And Digital in phase and quad phase channel produce sequence of phasing output for a given Fourier series. [3]

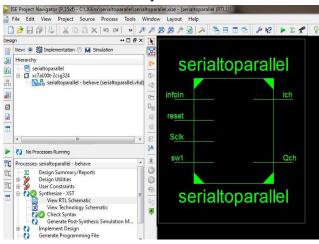

# E. Serial to Parallel Output

# TABLE-SERIAL TO PARALLEL

| Name of the<br>Terminals | Input /<br>Output | Description of the<br>Terminals                               |

|--------------------------|-------------------|---------------------------------------------------------------|

| Info in                  | Input             | Input info. Sequence                                          |

| Reset                    | Input             | Reset all the previous data                                   |

| Sclk                     |                   | Sine Clock                                                    |

| sw1                      | Input             | Sequential Width 1 which takes 2bit pair in transmitting data |

| i-ch                     | Output            | In phase channel output                                       |

| q_ch                     | Output            | Out phase channel output                                      |

Info in terminal provide in phase and out phase sequence at input side and produce Four array PSK output with different Fourier series.

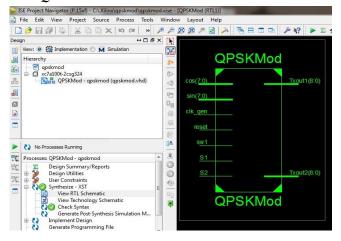

# F. QPSK Modulator

QPSK modulation modulates the four phase in which two phases are in and out and another two phases are the multiplication of in and out with sine and cosine term. And produce Four Fourier series which is known as 4- Array PSK.

## TABLE-QPSK MODULATION

| Name of the<br>Terminals | Input /<br>Output | Description of the<br>Terminals                               |

|--------------------------|-------------------|---------------------------------------------------------------|

| Cos (7:0)                | Input             | Input of cosine Fourier series                                |

| Sin (7:0)                | Input             | Input of sine Fourier series                                  |

| Reset                    | Input             | Reset all the previous data                                   |

| Clk_Gen                  |                   | Generate the Clock                                            |

| sw1                      | Input             | Sequential Width 1 which takes 2bit pair in transmitting data |

| S1                       | Input             | Output which perform as a third phase input                   |

| S2                       | Input             | Output which perform as a four phase input                    |

| Tx_out1                  | Output            | First two phase transmit at output 1                          |

| Tx_out2                  | Output            | Last two phase transmit at output 2                           |

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved

Output of sine cosine generator perform and apply to the QPSK Modulation. The bit stream of that Fourier series is sixteen maximum. This is divided into eight even odd formulation chains. S1 and S2 produce third and fourth phase string in a Four array PSK. Tx\_out1 and Tx\_out2 bring into being first two and last two series at the output. [5]

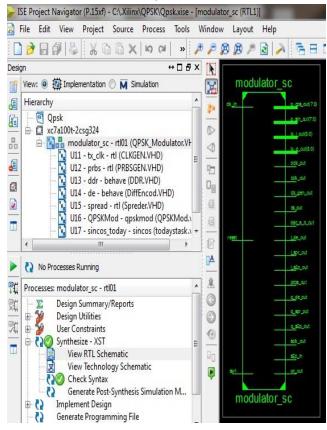

#### G. Core Modulation diagram

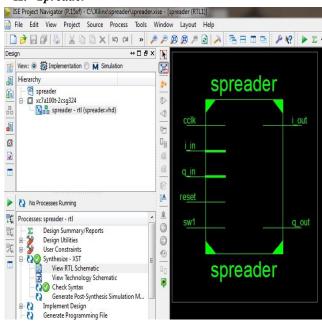

# H. Spreader

Final Four array Fourier series signals will add in the adder. And create Four Array PSK.

#### V. CONCLUSION

This Xilinx modulator predicts the RF subsystem output with modified modules. Four Array PSK performing on FPGA kit with Very High Speed Integrated Circuit Hardware Description Language.

This all Phenomenon perform under in ISE project navigator with mandatory and precise output.

## **REFERENCES**

- http://www.dsplog.com/2008/07/08/compare-bpsk-qpsk-4pam-16qa m-16psk-64qam-32psk/.

- http://www.mathworks.in/matlabcentral/newsreader/view\_thread/29 8247

- Wei-Long Sun "Data Sheet Simulation and RF path Modeling of a QPSK Radio Communication System" Kindle Edition, Publication Date March 26-2012.

- Syed WahajUI Haq; Shahzad Ahmed; Tehseen Sattar, "Differential QPSK based Communication System", Publication Date January 23-2013.

- Josua Bisuk Mubyarto Purba; Shelia Horan, "The Effect Of Pulse Shaping QPSK on Bandwidth Efficiency", Publisher: Biblioscholar, Creator: National Aeronautics And Space Administration.

- 6. Xilinx simulator guide.